微細化ゆえの「先端半導体」に起こる問題の解決へ。 新めっき技術によるナノスケール欠陥抑制効果を初めて確認

先端半導体の信頼性向上への貢献を期待

研究成果のポイント

概要

大阪大学産業科学研究所フレキシブル3D実装協働研究所と株式会社ダイセルは、奥野製薬工業の協力を得て、同社が開発しためっき技術「OPC FLETプロセス」を先端半導体基板(ビア径60μm)に適用し、内層銅と無電解めっき界面の断面を透過電子顕微鏡で詳細に解析しました。従来プロセスでは100nm以下のボイドを多数確認、OPC FLETプロセスでは界面ナノボイドはなく、ナノボイド発生を大幅に抑制できることを実証しました。更にこのナノボイド発生はめっき浴中へのニッケルの添加が大きく関与している可能性を突き止めました。これらの成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成事業「ポスト5G情報通信システム基盤強化研究開発事業」の結果得られたものです。

昨今、先端半導体パッケージのサブストレートは一層の微細化が進み、配線層の3次元化と微細化が同時進行、マイクロビアのサイズは50μmを下回り始めつつあります。ビア接続の微細化によって、信頼性が担保できない初期故障が世界で顕著になっており、影響は通信基地局、データセンタや宇宙航空機器、更には車載半導体など極めて広範囲に及んでいます。マイクロビアの断裂が引き起こすことから、”Weak-Micro-Via”問題(WMV)として、深刻な問題と捉えられています。WMV問題には様々な材料とプロセス因子が関与すると考えられますが、ナノスケールでかつ現象の複雑さから依然として原因が特定できておらず、製品の信頼性を担保する評価方法も存在しません。研究グループは、図1に示すようにマイクロビア底の数十nm厚さの無電解Cuめっき層周辺に初期からナノサイズのボイドが散在していることを突き止めており、このナノボイドの存在が最終製品に至るまでの熱履歴中に成長する可能性を見出していました。

一方、奥野製薬工業は先端半導体パッケージのビア小径化を想定し、無電解めっきの薄膜化及びビア底の内層銅との結晶連続性を達成できる「OPC FLETプロセス」を開発していました。

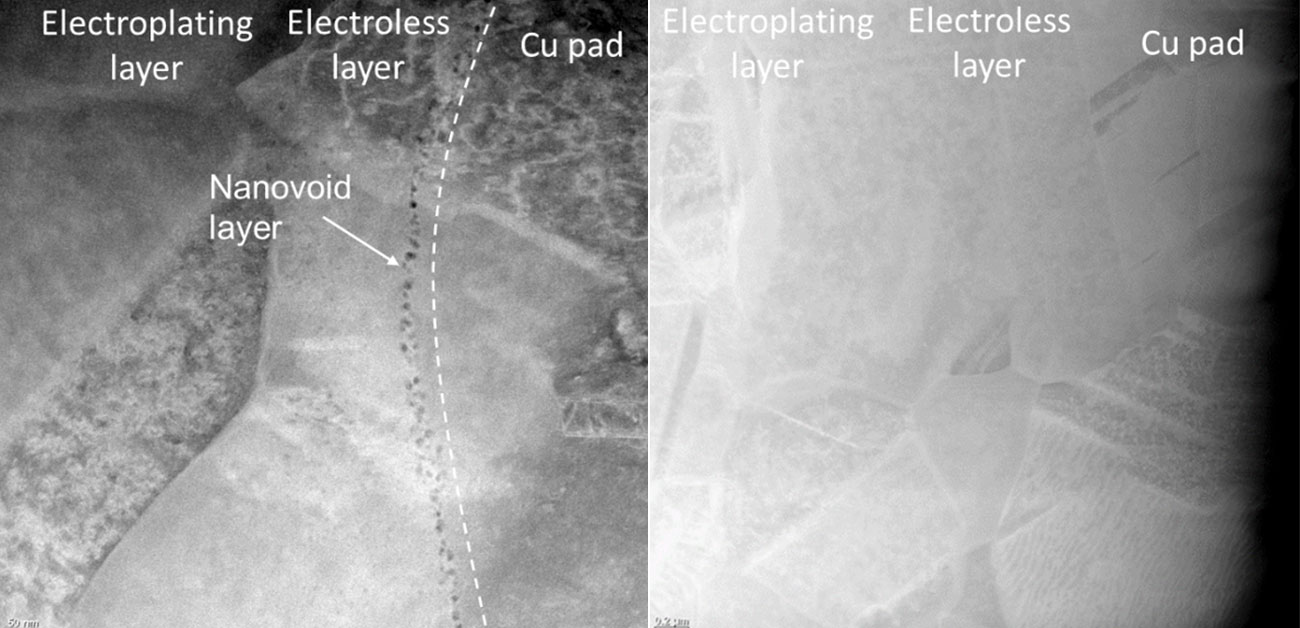

上記のような背景の基、我々は上記のナノボイド発生メカニズムを考察するため、ナノボイド発生部の分析を行い、図2に示すように無電解層にニッケルの共析を確認いたしました。従来のめっき浴にはニッケルが添加されているもののOPC FLETプロセスにはその特性上、ニッケルの添加はありません。ニッケルはめっき析出速度を向上させる効果があり、反応で発生した水素がナノボイドの起因になっていると考えました。これらの考察の基、OPC FLETプロセスを適用した先端半導体サブストレート(ビア径60μm)を試作いたしました。図3に示すように従来プロセスでは100nm以下のボイドを多数確認、OPC FLETプロセスでは界面ナノボイドはなく、ナノボイド発生を大幅に抑制できることを実証しました。更にこのナノボイド発生はめっき浴へのニッケルの添加が大きく関与している可能性が高いことも明らかになりました。

図1. マイクロビアと無電解めっき層中のナノボイド

図2. ナノボイド周辺部の分析結果

図3. 内層銅と無電解めっき界面の断面TEM像

本研究成果が社会に与える影響(本研究成果の意義)

本研究成果により、先端半導体のマイクロビア問題(初期及び経時故障)解決に大きく貢献します。その結果、先端半導体の信頼性向上への貢献が期待されます。

今後の目標

今回はナノボイド発生を大幅に低減できるめっきプロセスを見出しました。今後は奥野製薬工業の更なる協力を得て、ニッケルの関与の仕方やめっき反応速度を主に、ナノボイド発生メカニズムの全容解明に取り組みます。またナノボイドがマイクロビア問題解決に繋がることを検証いたします。

特記事項

本研究成果は以下の通り公開されました。

① Surface Mount Technology Associationn International Virtual Conference 2021, 11/15/2021 -12/31/2021

タイトル:Microstructure of weak-micro-via and its failure prevention

② International Conference on Device Packaging 2022, 3/7/2022 - 3/10/2022

タイトル:Improvement of micro-via reliability by using a new electroless Cu plating

参考URL

F3D HP:https://www.f3d.sanken.osaka-u.ac.jp/

ダイセルHP:https://www.daicel.com/

奥野製薬工業HP:https://www.okuno.co.jp/

SDGsの目標

用語説明

- ビア

部品を搭載しない、層間を電気的に接続する穴のこと。貫通基板では300μm径が主流であったが、ビルドアップ基板や極薄基板では、50μm径の穴も使われ始めている。

- ナノボイド

加工品等の内部に生じる空洞をボイド、特にナノスケールの大きさのボイドをナノボイドと称す。ナノとは 10 億分の 1 を表し、1nm は 1mm の百万分の 1、また 1μm の更に 1000分の1の長さである。

- サブストレート

半導体パッケージを構成する一部としての基板。電気的配線をした半導体、絶縁体の板のこと。チップをマウントしてボンディングなどで配線し、外部出力用端子を有する台座。