最小要素のチップレット集積技術を開発

広帯域接続と集積規模のスケーラビリティを実現

研究成果のポイント

- 広帯域チップ間接続性能と集積規模拡大に優れたチップレット集積技術を開発

- 微細な“MicroPillar”を用いたシリコン・ブリッジ接続構造と“All Chip-last”と呼ぶ製造プロセスによるチップレット集積技術を開発

- 汎用性の高いチップレット集積技術により、鈍化が見込まれる微細化に代わって今後の半導体集積回路システム技術の進化を加速

概要

東京工業大学 科学技術創成研究院 未来産業技術研究所の栗田 洋一郎 特任教授と共同研究企業による研究チームは、“Pillar-Suspended Bridge (PSB)”と呼ぶ技術を用いたチップレット集積技術を開発した。本技術は、今後の大規模なチップレット集積に求められる、広帯域のチップ間接属性能、チップレット集積規模の拡大といった要求を、最小限の構成と製造プロセスで実現するものである。

チップ間の広帯域接続には微細な“MicroPillar”を経由したシリコン・ブリッジ接続構造と、“All Chip-last”と呼ぶ製造プロセスを特徴としており、これらの構造とプロセスは、チップレット集積に求められる要求を最もシンプルな形で提供するものといえる。本技術は、今後の鈍化が見込まれる微細化に代わって、今後の半導体集積回路システム技術の進化を加速していくことが期待される。

本研究は10月1日に設立されたチップレット集積プラットフォーム・コンソーシアム(後述)に先駆け、アオイ電子株式会社、他4社と共同で実施されたもので、成果の詳細は10月3日(月)21時(日本時間)から開催される米国ボストンでの国際会議IMAPS 2022で発表された。

また、チップレット集積プラットフォーム・コンソーシアムは、東京工業大学の他、大阪大学産業科学研究所(菅沼 克昭 特任教授/大阪大学名誉教授)、東北大学(福島 誉史 准教授)を中心とし、企業32社が共同研究や協賛として参加予定(2022年9月現在)で、三次元集積技術、光集積技術などを含む、チップレット集積プラットフォーム技術全般の研究を対象としている。

研究の背景

半導体集積回路は20世紀中盤に発明されてから、ムーアの法則と呼ばれる、素子微細化/集積度向上による性能向上、消費電力とコスト低減により、世界のデジタル化の原動力となってきた。しかしながら、半導体回路のサイズが数nmまで微細化した近年においては、その半導体を構成する原子のサイズによる物理的限界により、その終焉が業界として認識されるようになっている。

一方で微細化に変わる集積規模拡大、性能向上/消費電力低減の新しい進化軸として、チップレット集積技術(図1)が注目を集めている。これは、主要なシステムを、従来の半導体実装技術に比べて密に結合された集積回路チップの集合体により構成するもので、半導体ウェハ/チップの物理的/製造技術的なディメンジョンを超え、かつ異なる機能・構造のものを大規模に集積するものである。これにより、従来の半導体集積回路技術では実現できなかった、異種構造集積による性能向上や、集積規模のスケーラビリティを提供することが可能になる。

図1. 従来の半導体集積回路とチップレット集積構造の比較

チップレット集積のためのプラットフォーム技術としてはこれまで、シリコン・インターポーザや、ポリマーベースのRDL (Redistribution Layer) インターポーザを用いた集積技術(RDL-first/Chip-last Fan-Outとも呼称)が開発・実用化されてきているものの、大規模な集積にはウェハサイズや製造技術による制限が指摘されている。一方で、シリコン・ブリッジとよばれる局所的に配置された高密度配線チップを用いる技術が大規模な集積に向けて開発されているが、その構造や製造プロセスの複雑性や高集積化のための製造精度の高さが課題となっている。

研究の成果

今回の研究は上記の背景と課題に鑑み、最小要素のチップレット集積構造/プロセスとして“Pillar-Suspended Bridge (PSB)” 技術を考案、コンセプト実証試作を行い、その実現性を立証した。図1、図2にPSBによるブリッジ接続構造を示す。チップレットとシリコン・ブリッジの接続部には “MicroPillar” と呼ぶ柱状金属のみが介在している。チップレット集積体はブリッジと共にモールド樹脂封止されており、シリコン・ブリッジ側のモールドを貫通する“Tall Pillar”により外部電極に接続する。本構造により、チップレット/ブリッジの最小限の接続構造によるチップ間接続密度や電気特性の向上、外部接続配線の高周波特性や放熱性能の改善が可能となる。また、ブリッジの配線の種類が選択可能であることや、集積規模拡大時の歩留まりの問題がなく(Known Good Bridge)、集積モジュールのサイズや製造単位を大型パネルなどへ拡大できるという利点がある。本構造は、製造工程における(1) All Chip-lastプロセスによる高い接合精度と製造工程中のダイ・シフト(モールド封止の際チップが動いてしまう現象)の抑制、(2) 線膨張(Coefficient of Thermal Expansion: CTE)の整合した接合プロセスにより実現した。

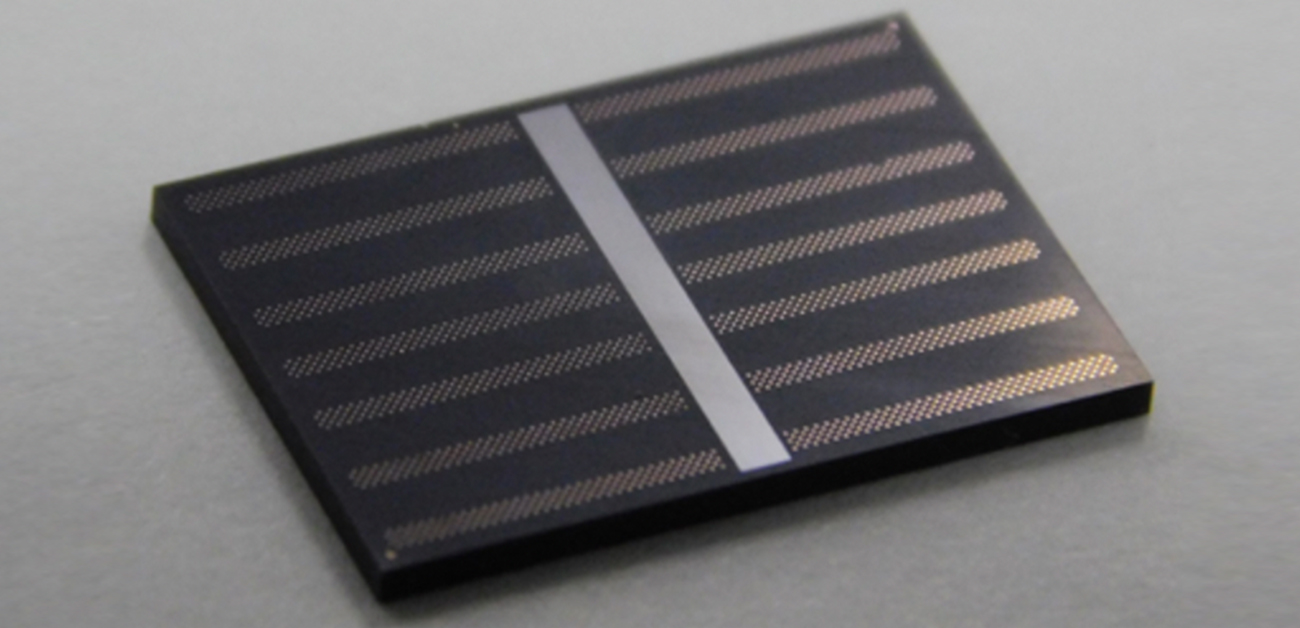

図2. PSBによるチップレット集積構造のコンセプト実証サンプルの外観

このように、PSB構造はブリッジ接続によるチップレット集積に関してシンプルで合理的な構造を有しており、これにFan-Out 機能を有する配線層(例えばRDL Interposer)を接続することで、図3に示すような理想的なチップレット集積パッケージや、図4に示すような大規模なチップレット集積システムを構成することができる。

図3. PSBモジュールの外部接続構造

図4. 大規模チップレット集積のイメージ

社会的インパクト

ムーアの法則による半導体集積回路微細化の鈍化が見込まれる中で、チップレット集積技術はシステム性能向上のための新しい進化軸として期待され、今後、プラットフォーム技術として長期的に人類社会に大きな影響を与えていくと共に、これに伴う巨大な関連産業の出現が予測されている。本技術やそれを構成する要素技術やアプリケーションは、これらに貢献することが期待される。

今後の展開

今後はこれらの接続密度向上/集積規模拡大、高性能ブリッジ配線技術、グローバル配線集積技術の開発、信頼性確認、システム適用検証などを行う予定である。

また、今回の研究を含むチップレット集積プラットフォーム技術全般を対象とし、製造技術/要素技術からアプリケーションに至るバリューチェーンでの研究開発とその産業化を目的としたチップレット集積プラットフォーム・コンソーシアムを2022年10月1日に設立した。コンソーシアムメンバーは東京工業大学の他、大阪大学(菅沼 克昭 特任教授/大阪大学名誉教授)、東北大学(福島 誉史 准教授)を中心とし、参加企業として、アオイ電子株式会社、アピックヤマダ株式会社、株式会社アルバック、青梅エレクトロニクス株式会社、奥野製薬株式会社、住友電気工業株式会社、住友ベークライト株式会社、太陽インキ製造株式会社、トーヨーケム株式会社、フォームファクター株式会社、マクセル株式会社、リンテック株式会社、FICT株式会社、他3社、協賛企業として、株式会社ディジタルメディアプロフェッショナル、株式会社トッパン・テクニカル・デザインセンター、株式会社NSCore、他13社が参加予定(2022年9月現在)で、三次元集積技術、光集積技術などを含む、チップレット集積プラットフォーム技術全般の研究を対象としている。

発表情報

学会:55th International Symposium on Microelectronics (IMAPS 2022)

論文タイトル:“Chiplet Integration by Die-to-Die Pillar-Suspended Bridge”

著者:Ichiro Kono, Shinji Wakisaka, Toshiaki Hirota, Takashi Saitou, Ken Ukawa, and Yoichiro Kurita

用語説明

- チップレット集積技術

「ムーアの法則」が集積回路(チップ)あたりの部品数が指数的に増加することを予測するのに対し、メタ的な観点から多数のチップレット(小さなチップ)を集積する技術が、ムーアの法則の効用であるシステム性能向上などを、微細化に代わり、もしくは補完する形で実現する技術体系。