Cosmic ray muon causes glitch in electronic devices

Toward the development of soft error technology for ensuring a safe and secure super smart society

Today’s advanced information society is supported by many high-performance and multifunctional electronic appliances produced by information and communications technology, so their malfunction could cause serious damage. Thus, in addition to improving the performance of devices, ensuring security and reliability over these devices has become crucial.

Electronic devices have become indispensable for our daily lives, with smartphones, personal computers, and even home appliances such as refrigerators all containing computer chips. However, ‘soft errors’ have attracted attention as one of the causes of malfunction in these electronic devices in recent years.

Soft errors are transient malfunction and breakdown which occur when electronic appliances are exposed to radiation (cosmic rays). One of the factors is a bit flip in a memory element of a semiconductor device, which is caused by neutrons that are generated by the clashing of cosmic rays with electronic appliances. Cosmic rays are radiation that reaches the Earth from space. The main components of cosmic rays (about 75 percent of charged particles) are muons. Muons have high penetrating power and can even pass through electronic appliances.

As the miniaturization and further reduction in power consumption of semiconductors progresses, radiation resistance of semiconductors has decreased. In addition to soft errors caused by cosmic ray-induced neutrons (measures against cosmic ray-induced neutrons have already been taken), soft errors by cosmic ray-induced muons have begun to be pointed out. Irradiation experiments with positively-charged muons (positive muons) had been reported, but irradiation experiments with negatively-charged muons (negative muons) had not.

Based on simulation research, it is predicted that effects of negative muons on soft errors are greater than those of positive muons because negative muons form muonic atoms with atomic nuclei. Thus, experimental verification of the impact of negative muons on soft errors has been sought after.

A group of researchers from Kyushu University, Osaka University, Institute of Materials Structure Science, Japan Proton Accelerator Research Complex (J-PARC), and Japan Atomic Energy Agency conducted irradiation experiments with the strongest positive and negative muon beams that can be generated by the Muon Science Facility (MUSE) at the Materials and Life Science Facility (MLF) in J-PARC.

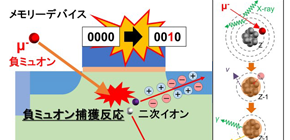

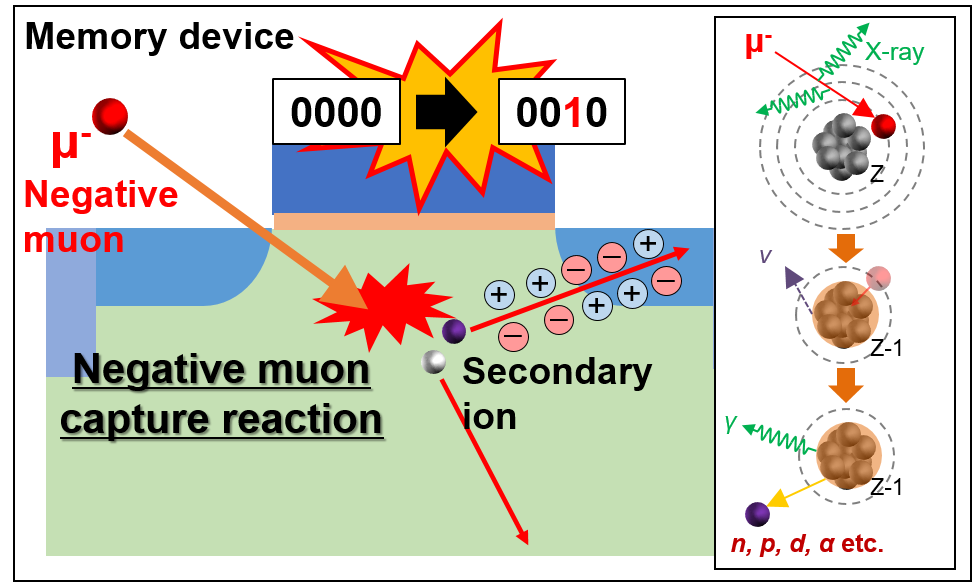

In this study, it was clarified that low-energy muons that stopped in semiconductors had greater effects on the occurrence of single event upsets (SEUs, a bit flip in a memory element of a semiconductor device), especially negative muon SEUs, which occur at a higher rate than positive muon SEUs. This is caused by negative muon capture reactions at places where negative muons stop.

Results of irradiation experiments of negative muons had not been previously reported. Correct evaluation of soft errors and measures against them will be helpful in creating a super smart society achieved by the development of the Internet of Things (IoT). Moving forward, safe and secure semiconductor technology for automatic driving and IoT technology will be developed by accumulating test data, establishing evaluation technology of soft error rates (SERs) through the improvement of simulation techniques, and applying the technology to designing next-generation semiconductor devices.

Abstract

We have performed an irradiation test of low-energy positive and negative muons on 65-nm ultra-thin body and thin buried oxide silicon-on-insulator static random access memories. The single event upset (SEU) cross sections were measured systematically as a function of incident muon momentum and operating supply voltage. The experimental results show that the negative muon SEUs occur at about three times higher rate than the positive muon ones at the supply voltage of 0.5 V when the incident muons stop near the sensitive volume (SV). A Monte-Carlo simulation with the particle and heavy ion transport code system (PHITS) was carried out using a simple SV model. The simulation based on the PHITS using the SV model is found to reproduce generally well the momentum dependence of the measured SEU cross sections for both positive and negative muons. From the simulation, the charged particles and secondary ions having significant influence on SEUs are specified and the differences between negative and positive muons are discussed.

Figure 1. Negative muon penetrates into semiconductor memory device, generates secondary ion, such as proton and alpha particle, through negative muon capture reaction and causes bit upset due to deposited charge. (Credit: Kyushu University)

Figure 2. An example of measurement results of SOTB (silicon on a thin buried oxide) SRAM at 0.5 V operation. Red and blue symbols represent relative bit upset probability due to negative muon and positive muon, respectively. Y-axis is in log scale. Muons whose momentum is 38MeV/c stop near memory transistors and deposit larger charge resulting in frequent bit upsets. Negative muon generates secondary ion through negative muon capture reaction, and hence it has four times higher bit upset probability than positive muon. (Credit: Kyushu University)

To learn more about this research, please view the full research report entitled " Negative and Positive Muon-Induced Single Event Upsets in 65-nm UTBB SOI SRAMs " in IEEE Transaction on Nuclear Science , https://doi.org/10.1109/TNS.2018.2839704 .

Related links