量子コンピュータの実用化を早める 新たな量子計算アーキテクチャを確立

一万程度の中規模な物理量子ビット数でも高精度な量子エラー訂正を実現

概要

国立大学法人大阪大学(以下、大阪大学)量子情報・量子生命研究センターと富士通株式会社(以下、富士通)は、このたび、量子コンピュータの実現に不可欠な量子エラー訂正に必要な物理量子ビット数を大幅に低減することで、現行コンピュータの計算性能を超える量子コンピュータの実用化を早めることが可能な高効率位相回転ゲート式量子計算アーキテクチャを確立しました。

従来の誤り耐性量子計算(FTQC)アーキテクチャでは、量子エラー訂正に大量の物理量子ビットが必要になるため、100万以上の物理量子ビットを有する量子コンピュータでなければ実用化が困難と言われています。そのため、物理量子ビット数が今後1万程度に到達した段階で量子エラー訂正を実行しても計算可能な規模は極めて小さく、現行のコンピュータの処理能力を超えることは不可能と考えられていました。

これまでのアーキテクチャでは、量子エラー訂正した4つの基本量子ゲートの組み合わせにより量子計算を実行しており、そのうち1つの基本量子ゲートには量子エラー訂正に大量の物理量子ビットが必要でしたが、今回両者は、その基本論理ゲートを代替する手法を開発し、従来の1割の物理量子ビットで量子エラー発生を大幅に抑えられることを確認しました。これにより、1万物理量子ビットがあれば、現行コンピュータにおける最高性能の約十万倍に相当する64論理量子ビットの量子コンピュータを構築することが可能となります。

両者は今後、本量子計算アーキテクチャを発展させてEarly-FTQC時代の量子コンピュータ開発を主導していくとともに、材料や金融領域などの実問題への早期適用を目指していきます。

開発の背景

量子ゲート方式の量子コンピュータは、現行のコンピュータと比較していくつかの領域で飛躍的に計算速度が向上すると見込まれており、様々な課題への適用が期待されています。量子コンピュータが真の性能を発揮するには、複数の物理量子ビットから1つの論理量子ビットを形成し、量子ビットに冗長性を持たせることで、発生した量子エラーを訂正しながら計算する量子エラー訂正技術が鍵となります。

従来のFTQCでは、CNOT、H、S、Tという4つの基本量子ゲートそれぞれに対して量子エラーを訂正し、それらの基本量子ゲートを組み合わせることで、あらゆる量子計算を量子エラーの影響なく実行可能とする方針のアーキテクチャが主流です。しかし、特にTゲートの量子エラー訂正には非常に多くの物理量子ビットが必要であり、さらに量子計算に含まれる状態ベクトルの向き(位相)を回転させる操作には、論理Tゲート操作を平均して50回程度繰り返す必要があります。このため、FTQCが可能な本格的な量子コンピュータには100万以上の物理量子ビットが必要と言われており、その実現には相当な年月が掛かることが予想されています。

大阪大学と富士通は、大阪大学の「量子情報・量子生命研究センター(Center for Quantum Information and Quantum Biology)」内に2021年10月1日に設置した「富士通量子コンピューティング共同研究部門」において、富士通が推進する「富士通スモールリサーチラボ」 の一環として量子エラー訂正技術の研究開発に取り組んでおり、このたびEarly-FTQC時代に向けた新たな量子計算アーキテクチャを確立しました。

高効率位相回転ゲート式量子計算アーキテクチャについて

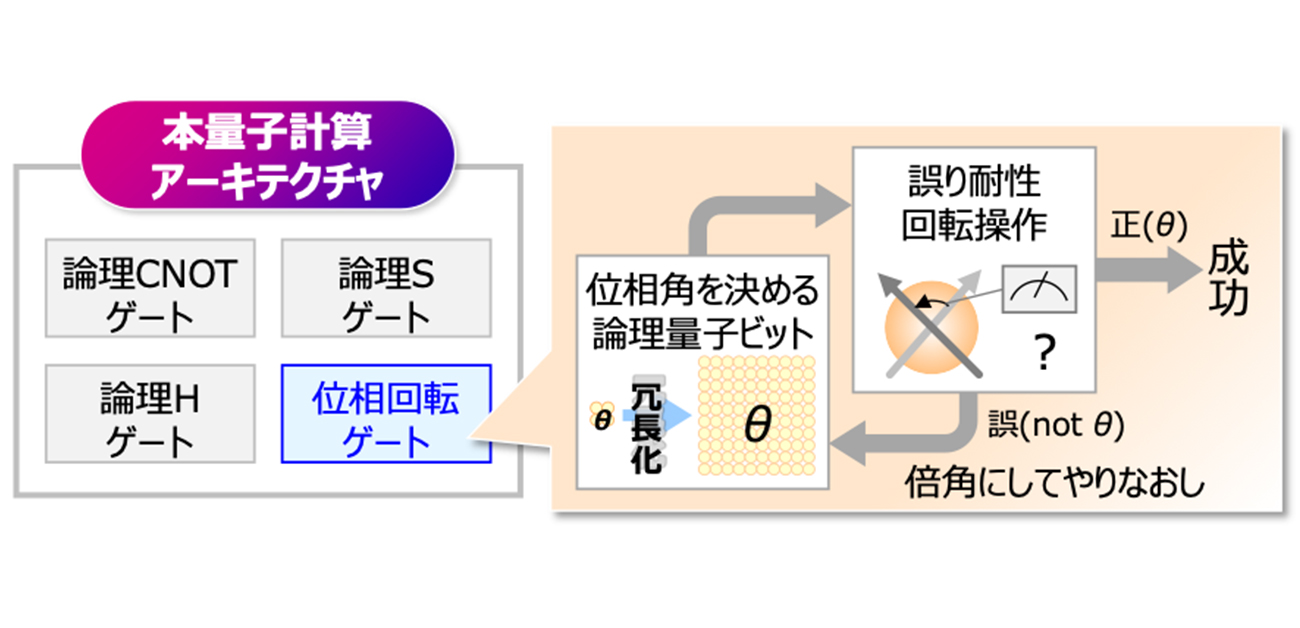

今回確立した量子計算アーキテクチャでは、基本量子ゲートセットを新たに定義し、特に大量の物理量子ビットと量子ゲート操作が必要であった位相回転操作を高効率で実行する位相回転ゲートを世界で初めて導入します。

具体的には、大量の物理量子ビットを使用する論理Tゲート操作を繰り返す従来アーキテクチャとは異なり、任意の角度を直接指定して位相回転するゲート操作を実行します。これにより、物理量子ビットを従来の1/10以下に低減するとともに、任意回転の実行に掛かるゲート操作回数を従来の1/20程度に低減することができます。また、本量子計算アーキテクチャでの量子エラー確率は、物理量子ビットでの量子エラー確率の約1/8まで抑え込めることが確認でき、非常に高精度な計算を可能にします。

本量子計算アーキテクチャにより、1万物理量子ビットに対して64論理量子ビットの量子コンピュータを構築可能であり、その計算性能は現行コンピュータの最高性能の約十万倍に相当します。このように現行のコンピュータを超える計算性能を従来の1/10以下の大幅に少ない物理量子ビットで実現できるため、本格的な量子コンピュータの到来を飛躍的に早めることができます。

図. 本量子計算アーキテクチャのイメージ

なお、本量子計算アーキテクチャの確立のための研究は、国立研究開発法人 科学技術振興機構(JST)共創の場形成支援プログラム(COI-NEXT)「量子ソフトウェア研究拠点」(JPMJPF2014)、JST ムーンショット型研究開発事業 ムーンショット目標6「2050 年までに、経済・産業・安全保障を飛躍的に発展させる誤り耐性型汎用量子コンピュータを実現」 研究開発プロジェクト「誤り耐性型量子コンピュータにおける理論・ソフトウェアの研究開発」(JPMJMS2061)、文部科学省 光・量子飛躍フラッグシッププログラム(Q-LEAP)「知的量子設計による量子ソフトウェア研究開発と応用」 (JPMXS0120319794)および「量子コンピュータのための高速シミュレーション環境構築と量子ソフトウェア研究の展開」(JPMXS0118067394)による助成を受けて行われました。

関連リンク

・大阪大学と富士通、誤り耐性量子コンピュータの研究開発体制を強化(2021年10月1日 大阪大学、富士通連名プレスリリース):https://www.osaka-u.ac.jp/ja/guide/public-relations/press_release/2021/10/20211001_02

・大阪大学量子情報・量子生命研究センター:https://qiqb.osaka-u.ac.jp/

・Fujitsu Quantum:https://www.fujitsu.com/jp/about/research/technology/quantum/

・富士通スモールリサーチラボ:https://www.fujitsu.com/jp/about/research/srl/

・記者説明会の動画サイト:https://youtu.be/qc8SgoLQtdM

用語説明

- 物理量子ビット

量子コンピュータの物理的な構成要素であり、量子情報を担う最小単位

- FTQC

Fault-Tolerant Quantum Computationの略語で、量子エラーを訂正しながら誤りなく量子計算を実行すること

- 基本量子ゲート

それらの組み合わせによりあらゆる量子計算が可能となる複数の量子ゲート。現行コンピュータのAND、XOR、NOTゲートに相当

- 論理量子ビット

複数の物理量子ビットで構成され、冗長化により量子エラーを訂正された論理的な最小単位

- Early-FTQC時代

1万程度の物理量子ビットしか実装できておらず、FTQCが実現できないと考えられている時代