次世代の FPGA チップに。 トランジスタを用いず12倍の高密度化実装に成功

研究成果のポイント

・新ナノデバイスをFPGAのプログラム機能実現に利用することで12倍の実装密度向上に成功

・FPGAは、ユーザーが論理機能を自由にプログラムできる半導体チップである。機能実現までに必要な設計期間が短く、日進月歩で開発が進むAIアプリケーションの実現プラットフォームとして注目

・従来のFPGAでプログラム機能実現に必要だったシリコン面積を不要に

・最先端AIアルゴリズムの短期間・高性能実装プラットフォームとして期待

概要

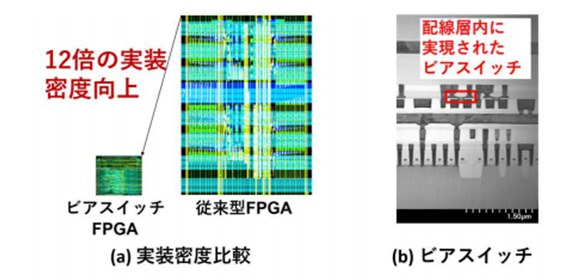

大阪大学大学院情報科学研究科の橋本昌宜教授らの研究グループは、新ナノデバイスであるビアスイッチ をFPGA(Field Programmable Gate Array)のプログラム機能実現に利用することで、FPGAチップの12倍の高密度化実装に世界で初めて成功しました (図1(a)) 。また、AIアプリケーションに適したFPGAアーキテクチャを開発し、5倍のエネルギー効率向上が期待できること、半導体微細プロセスの採用により継続的な性能向上が期待できることを明らかにしました。

これまでのFPGAは、プログラム機能の実現にトランジスタを多数利用しており、チップの低密度化、低性能化を招いていました。

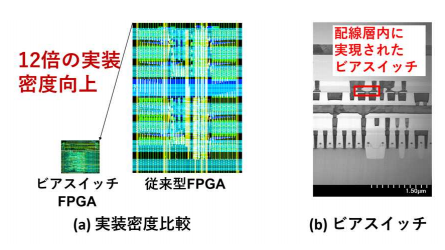

今回、橋本教授らの研究グループは、トランジスタを用いずに配線層内に配置したビアスイッチ (図1(b)) を用いてプログラム機能を実現するビアスイッチFPGAチップの開発に成功し、12倍の実装密度 向上を達成しました。最小線幅65nmのシリコンCMOSプロセスを用いた試作FPGAチップに所望のプログラムができることを確認しました。最先端AIアルゴリズムを短期間で高性能に実装できるプラットフォームとしての利用が期待されます。

本技術の詳細は、2月18日(火)1:30(日本時間)に米国サンフランシスコで開催される半導体技術に関する最大の会議である「国際固体素子回路会議ISSCC2020(IEEE International Solid-State CircuitsConference 2020)」で発表しました(ISSCC発表番号33.3)。

図1 開発したビアスイッチFPGAの実装密度向上と配線断面

研究の背景

これまでFPGAは、短期間で機能実現でき、少量多品種の製品に適するという特徴により利用拡大が進んできました。しかし、チップ内のプログラミング機能の実現に多数のトランジスタを利用するため、チップの実装密度が低く、動作速度や消費電力などの性能が低いという課題がありました。

橋本教授らの研究グループでは、ビアスイッチと呼ぶ新しい不揮発スイッチデバイスの開発を進めてきました。今回、ビアスイッチを用いたFPGAの試作に世界で初めて成功し、従来のトランジスタでプログラム機能を実現するFPGAに対して、12倍の実装密度向上を実証しました (図1(a)) 。実装密度はFPGAチップの価格に直結するため、大幅なコスト低減が期待できます。また、プログラム機能の実現にトランジスタを利用しなくなったため、全てのトランジスタをコンピューティングに利用できるようになり、高いコンピューティング性能の実現も可能となります。最小線幅65nmのシリコンCMOSプロセスを用いて製造したFPGAチップをプログラミングし、期待通りの機能が実現できていることを確認しました。ビアスイッチが次世代のFPGAに適したデバイスであることを明らかにしました。

さらに、AIアプリケーションが効率的に実現できるFPGAアーキテクチャを開発し、その性能予測を行いました。トランジスタを用いてプログラミング機能を実現したFPGAに対して、5倍のエネルギー効率向上が可能であることもわかりました。最小線幅7nmのシリコンCMOSプロセスで製造した場合、さらに11倍のエネルギー効率向上が期待できます。

本研究成果が社会に与える影響(本研究成果の意義)

本研究成果により、AIアプリケーションを実現するプラットフォームとして期待が集まるFPGAデバイスの性能ならびにエネルギー効率を向上させることができます。さらに高密度化により、FPGAデバイスの低価格化も期待できます。

特記事項

本研究成果は、2020年2月18日(火)1:30(日本時間)にISSCC2020(IEEE International Solid-State Circuits Conference 2020)で発表しました。

タイトル:“Via-Switch FPGA: 65nm CMOS Implementation and Architecture Extension for AI Applications”

著者名:M. Hashimoto, X. Bai, N. Banno, M. Tada, T. Sakamoto, J. Yu, R. Doi, Y. Araki, H. Onodera, T. Imagawa, H. Ochi, K. Wakabayashi, Y. Mitsuyama, T. Sugibayashi

なお、本研究は、JST戦略的創造研究推進事業CRESTの一環として行われ、日本電気株式会社杉林直彦技術主幹、若林一敏シニアエキスパート、京都大学大学院情報学研究科小野寺秀俊教授、立命館大学情報理工学部越智裕之教授、高知工科大学システム工学群密山幸男准教授らからなる研究グループで実施しました。

参考URL

大阪大学 大学院情報科学研究科 情報システム工学専攻 集積システム設計学講座 橋本研究室

http://www-ise1.ist.osaka-u.ac.jp/lab/

用語説明

- ビアスイッチ

配線層内に実現された不揮発スイッチ(原子スイッチ※3)とプログラム用の選択デバイス(バリスタ )からなるデバイス。プログラムを制御するためのアクセストランジスタが不要のため、配線層内に小面積で実装できる特徴を持つ。

- 実装密度

チップの単位面積あたりにプログラムできる量。ユーザーが論理機能を自由にプログラムできる半導体チップ。機能実現までに必要な設計期間が短く、日進月歩で開発が進むAIアプリケーションの実現プラットフォームとして注目が集まっており、各社が提供するクラウドサービスでも活用が進んでいる。

- 原子スイッチ

スイッチ機能と不揮発メモリ機能を合わせ持ったスイッチデバイス。金属原子が固体電解質内を移動してスイッチするため、低抵抗で低入力容量という特徴を持つ。

- バリスタ

格子構造上に配置されたビアスイッチアレイに対して、選択したビアスイッチのみをプログラムするために導入された素子。低電圧印加時に抵抗が高く、高電圧印加時に抵抗が低くなる。