超高精度3次元回路シミュレーターの開発に成功

電磁ノイズが生じない回路のレイアウト設計が可能に

研究成果のポイント

・電子・電気機器の誤動作や発熱の原因となる電磁ノイズを超高精度に定量化するためのシミュレーターを開発。

・設計段階で電磁ノイズの発生箇所を特定することが可能に。

・特異構造を持つ次世代の高性能回路部品の設計へと応用可能。

概要

大阪大学大学院基礎工学研究科の大学院生の神野崇馬さん(博士後期課程3年、特別研究員DC2)と木虎秀二さん(博士後期課程3年)、土岐博特任教授(本学名誉教授)、阿部真之教授は、回路基板内に発生する電磁ノイズ現象を超高精度に再現するシミュレーターを開発することに成功しました。本研究成果は、2019年11月29日に国際論文誌「Scientific Reports」(オンライン)に掲載されました。

研究の背景

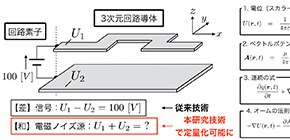

私たちの身の回りのほとんどの機器は電気で動き、制御されています。電磁ノイズはそれらの内部で発生し、誤動作や温度上昇などの様々な問題を引き起こしています。電気回路は電気を通す導体で構成され、そこに電気を流すことで信号や電力などを送ることができます。例えば、我々の日常生活では、100Vのコンセントにプラグを挿すことで電化製品を動かすことができます。この時、プラグを構成する2つの導体の間には100Vの電圧、つまり電位の「差」がかかり、製品内の電気回路が駆動します。しかし、電磁ノイズは我々が普段気にしていない電位の「和」が起源となって生じています (図1) 。電磁ノイズの起源である電位の「和」がなぜ、どこで、どのように生じ、電気回路に影響を及ぼすのかを可視化することは困難であるため、それらの対策の多くは熟練技術者の経験やノウハウを元に施されております。私たちの生活は電気で制御された機器の普及によりますます便利になりますが、それに伴い電磁ノイズによる問題が生じるリスクも大きくなります。よって、電磁ノイズの発生過程を可視化し、どのように生じているのかを理解することは次世代回路設計において非常に重要なことであります。そこで、研究グループではこれまでに、電気・電子回路内に発生する電磁ノイズ現象を定量化する理論を考案し、電磁ノイズが発生しない回路構造を理論的に導出しました。

図1 本研究技術の概略図

3次元回路導体に回路素子を繋げ、信号を入力した時の物理量の時間変化を定量化することが可能(図は平面であるが立体も可能)。また、電磁ノイズの起源である和の成分も定量化可能に。

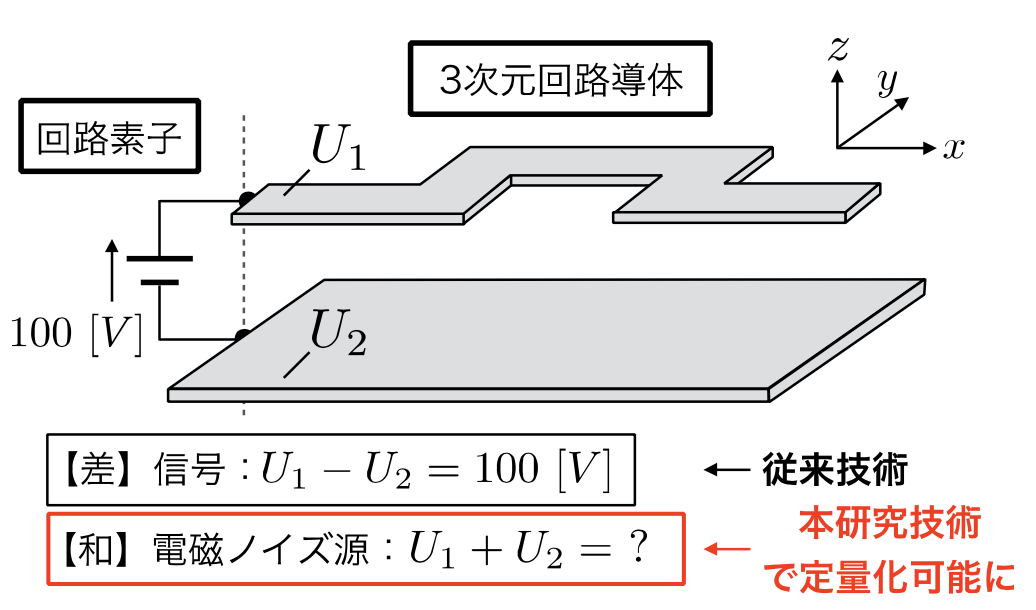

図2 本研究で用いる方程式と変数

電磁気学で用いられる物理量を変数として計算する。1と2はマクスウェル方程式から得られるポテンシャルを表しており、その源は電荷と電流である。また、電流と電荷の関係を3の連続の式用い、ポテンシャルと電流が満たす関係式をオームの法則を用いて表している。これらの方程式を連立して解くことにより、回路内の現象を記述することができる。

研究の内容

本研究では、電磁ノイズ現象を記述するために、回路の特性を導体間の相対的な物理量である「差」で表すのではなく、それぞれの導体内の絶対的な物理量を定量化し、「和」を扱うことを可能にしたことで、電磁ノイズ現象の起源を解明するシミュレーターを開発することに成功しました。具体的には、回路を構成する3次元導体内の電磁気学的な物理量である電位と電荷、ベクトルポテンシャル、電流を変数とする連立偏微分積分方程式を物理モデルによる近似などを用いずに、直接解く数値計算手法を考案しました。さらには、導体内の物理量を励起するために、任意の境界で回路素子(電圧源や抵抗など)を接続するアルゴリズムを開発しました。

今回の研究成果により、電気回路内の物理量が時間に伴いどのように伝搬し、変化するのかを可視化することができるようになります(本論文のSupplementary Information参照)。それにより、電磁ノイズがなぜ、どこで、どのように生じたのかを直感的に理解することができ、これまでの対症療法的な電磁ノイズ対策ではなく、電磁ノイズの起源を根本からなくす回路設計が可能になります。

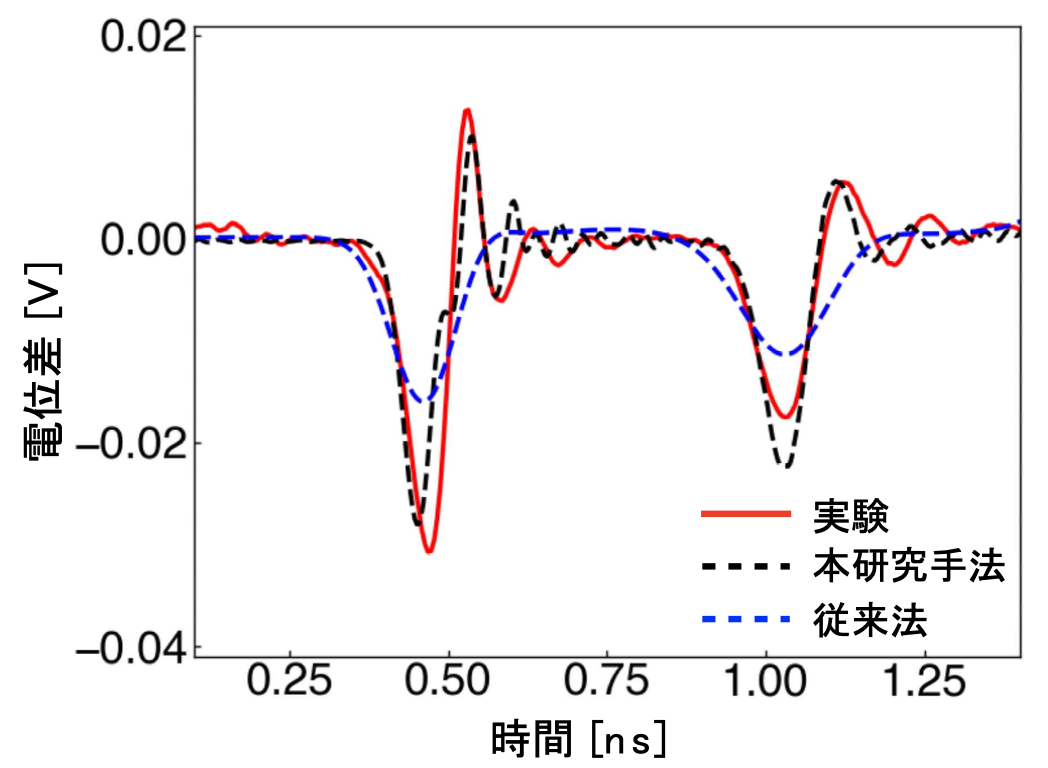

本研究技術は、回路の特性を決める導体形状を高精度に考慮することができます。実証実験では、本研究技術は実験の波形を良く再現していることがわかります (図3) 。これは、回路の配線の曲げによって伝搬する信号(電位差)が歪んでおり、この歪みの形状は回路の形状を反映しているため、本研究成果は回路の形状を高精度に考慮できることがわかります。また、1ナノ秒以下の高速信号にも対応していることがわかります。今後は本研究技術を用いて、我々が普段用いる様々な回路導体内に発生する電位の「和」によって発生する電磁ノイズ現象を解明し、ノイズレス回路設計へと応用していきます。

図3 実験結果と本研究手法と従来法で得られた数値計算結果

電位差が0の時は電磁ノイズが発生していない時を表しており、生じた電位差は回路の配線の曲げによって生じた電磁ノイズを表している。本研究手法は実験をよく再現していることがわかる。

本研究成果の今後の展開

神野崇馬さんと木虎秀二さん、土岐博特任教授(本学名誉教授)、阿部真之教授は電磁ノイズのないノイズレスインフラを実現し、機器の性能改善だけでない、「超低消費電力」で「超低廃熱」という高付加価値の機器を利用できる社会の実現を目指しています。具体的には、ノイズレスな構造を理論的に明らかにし、「電磁ノイズの革新的低減による低消費電力化にブレークスルーをもたらすことができる」というPOC(Proof Of Concept)の実証を目指しています。本手法が先端技術を汎用技術へと展開し、ノイズレスインフラの考えが、社会的・経済的にインパクトのある事業に育つための指針を得ることに挑戦しています。

ノイズレスインフラの実現に向けた活動を積極的に進め、基礎研究としての電磁ノイズの研究と、社会実装に向けた電磁ノイズが低減される機器に関する応用研究を行いたいと考えています。ノイズレスインフラの考えは社会のあらゆる場面でいろいろなアイデアが出てくることを期待しており、基礎研究の段階から本学共創機構産学共創本部と協力しながら、多くのパートナーを探していきたいと考えています。研究だけでなく知的財産権取得に向けた取り組みを今後も積極的に行います。

特記事項

本研究成果は、2019年11月29日に国際論文誌「Scientific Reports」(オンライン)に掲載されました。

タイトル:“Time-domain Formulation of a Multi-layer Plane Circuit Coupled with Lumped-parameter Circuits using Maxwell Equations”

著者名:Souma Jinno, Shuji Kitora, Hiroshi Toki, and Masayuki Abe

論文URL: https://www.nature.com/articles/s41598-019-53288-x

研究者のコメント

本論文はこれまでの簡易な物理モデルを用いた電磁ノイズ定量化手法とは全く異なるアプローチをしており、電磁ノイズを純粋な物理現象として解明したいというモチベーションの元に作成されました。今回発表した内容は、3次元回路における数値計算のための方程式の導出とその計算アルゴリズムです(特許出願済み)。これを用いることで、様々な電気・電子回路に配線された導体形状が原因で生じる電磁ノイズ現象の発生過程を可視化することが可能になります。これを用いると、設計段階での電磁ノイズレス化や、次世代の高周波回路で用いられる幾何学的な特異形状を有するレイアウト設計への応用の可能性があります。

参考URL

大阪大学 大学院基礎工学研究科 附属極限科学センター 阿部研究室HP

http://www.ae.stec.es.osaka-u.ac.jp/wp/